January, 1993 UM-DVME-601

# **CAUTION**

Do not apply power to this board until you have read this manual

## Unpacking

This product should include a DVME-601 board in a static-protective bag, and a User Manual. Upon receipt, carefully remove the board from the anti-static bag and visually inspect the board for physical damage which may have occurred in shipment. In the event of damage, save all packing materials for inspection by your carrier to validate shipping damage claims. Should the board need repair at a later date, it may be safely returned in its original packing materials. If you do not intend to use the board immediately, store it in the anti-static bag until use.

CAUTION - Always store the board in the anti-static bag

This board contains components that can be damaged by static discharge and should be handled with caution. Make sure your body is earth grounded before handling the board, especially in dry, low humidity conditions. Avoid board contact with clothing having a high synthetic content. Avoid contact after walking across carpeting. Before you first touch the board, continuously hold the VME chassis it will be installed into. In severe static discharge environments, consider grounding wrist straps or other protective measures.

## Warranty

This board was precision manufactured with the highest quality methods. DATEL warrants that this product was manufactured free of defects in workmanship or materials under normal use and service as described in the literature for this product. Obligations under this warranty are limited to replacing or repairing, at DATEL's option, any of said products, at DATEL's factory or facility, transportation charges prepaid, and which are, after examination disclosed to the satisfaction of DATEL to be thus defective, for a period within one year of shipment. This warranty shall not apply to any such products which have been repaired or altered except by DATEL or which have been subject to misuse, negligence or accident. In no case shall DATEL's obligation exceed the original purchase price. The aforementioned provisions do not extend the original warranty period of any product which has either been repaired or replaced by DATEL. This warranty does not contain a guarantee, either expressed or implied, of merchantability or fitness for a particular purpose. DATEL cannot assume liability for damage or loss as a result of the use of this product. It is the customer's sole responsibility to determine if this product is suitable for his or her application.

# Disclaimer

All information contained in this document has been carefully examined and is believed to be entirely accurate. However, DATEL assumes no responsibilities for errors or omissions. DATEL reserves the right to make changes to this manual without prior notification in accordance with DATEL's policy of product support and improvement.

## **Proprietary Notice**

The information and the design of this product are the exclusive property of DATEL. This entire document is proprietary to DATEL and shall not be disclosed to third parties without the express written consent of DATEL. This information is not to be photocopied, transcribed, recorded, communicated or reproduced by any means without permission. The foregoing does not apply to vendor proprietary rights or rights under the patents of third parties. Use of this product does not convey a license, either expressed or implied.

Copyright © 1990 by DATEL

#### Quick Reference Guide

#### **Serial Port Monitor Commands**

Carriage return terminates all commands and parameters. See section 3. Exit Modify commands with ".<cr>"

Command Function

H Display Help menu.

RD Display all 68010 internal registers.

RM <reg> Display/Modify cycled CPU registers.

RI [offset](reg) Display/Modify offset indirect memory.

MD <start adrs> Display block of memory in hex and ASCII.

[<end adrs>] or [,<count>]

MM <start adrs> Display/Modify memory. ".<cr>" to exit.

BF <start adrs> Fill memory with "data".

<end adrs> <data>

BR <br/>break adrs> Set break point and optional count.

[,<count>]

BR Display break point and count.

NOBR Delete all break points.

T [<start adrs>] Trace "count" instructions (default = 1)

[,<count>] beginning at current PC or "start adrs".

G [<start adrs>] Execute from PC or adrs if EXEC ON.

EXEC ON Go to Exec level (Awake) for DPR commands.

EXEC OFF Go to MONITOR level and ignore DPR.

Control-C If at EXEC level, go to MONITOR level but stay Awake. Halts running

program.

AD <start addr> Display continuous A/D conversions. ^S

[,<final adrs>] to pause, ^Q to resume, <cr> to stop.

SRDL Start serial port download. ^X to abort.

Control-X Hard reset to Monitor. Abort locked CPU.

TC Load. chan. adrs. reg. with 00->FF bytes CT <adrs> Write continuous 00->FF byte at memory.

# **Table of Contents**

| Sectio                                                                                                                                  | on 1 - General Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1.0<br>1.0.1<br>1.0.2<br>1.0.3<br>1.0.4<br>1.0.5<br>1.1                                                                                 | Introduction Scope of This Manual Who This Manual Is Intended For Related Information Equipment Requirements Implementation Procedure Description DVME-601 Specifications                                                                                                                                                                                                                                                                                                                                                                                                        | 1-1<br>1-1<br>1-1<br>1-2                  |

| Sectio                                                                                                                                  | on 2 - Board Configuration and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |

| 2.0<br>2.0.1<br>2.0.2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.5<br>2.5.1<br>2.5.2<br>2.6<br>2.7<br>2.8              | Determining Your Host Environment Host Memory Map Compatibility Host Interrupt Compatibility Base Address Selection Address Modifier Selection Interrupt Level Selection A/D Converter Jumpering Single-Ended/Differential Inputs Instrumentation Amplifier Gain Selection A/D Input Range and Output Data Coding Selection A/D Input Range and Output Data Coding Selection Auxiliary RS-232-C Serial Port Jumpers RS-232-C Serial Port Handshakes RS-232-C Auxiliary Software Serial Port Analog and Digital Ground Connection EPROM Memory Address Jumpers Board Installation | 2-12-22-42-52-52-62-72-82-92-102-10       |

| Sectio                                                                                                                                  | on 3 - I/O Connections and the Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

| 3.0<br>3.1<br>3.1.1<br>3.2<br>3.2.1<br>3.3<br>3.4<br>3.5<br>3.5.1<br>3.5.3<br>3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6 | Introduction Local Analog Signal Inputs Typical Analog Input Wiring A/D Channel Expansion Bus Channel Expansion Multiplexer Boards VMEbus Connections Peripheral I/O Connections Monitor Terminal Connections RS-232-C Terminal Cable Monitor Control Characters Monitor Commands Power Up Activity Notation and Syntax Monitor Command Listing Display/Modify Commands Command Familiarization Hardware Reset                                                                                                                                                                   | 3-13-33-43-53-73-83-93-113-123-133-143-17 |

# Section 4 - Programming Introduction

| 4.0     | General Procedure                                        | 4-1           |

|---------|----------------------------------------------------------|---------------|

| 4.1     | Operation with No Local User Program                     | 4-2           |

| 4.2     | Memory Map and Internal Architecture                     | <i>1</i> -3   |

| 4.2.1   | Dual Port RAM Organization                               | 15            |

| 4.2.2   | Interrupt Registers                                      | 4-0<br>4-6    |

| 4.2.3   | Local Registers                                          | 4-7           |

| 4.3     | Data Acquisition Registers and General Procedure         | 1-8           |

| 4.3.1   | Analog Channel Addressing                                | 4-10<br>4-10  |

| 4.3.2   | Left Justified A/D Data                                  | 4-10<br>4-19  |

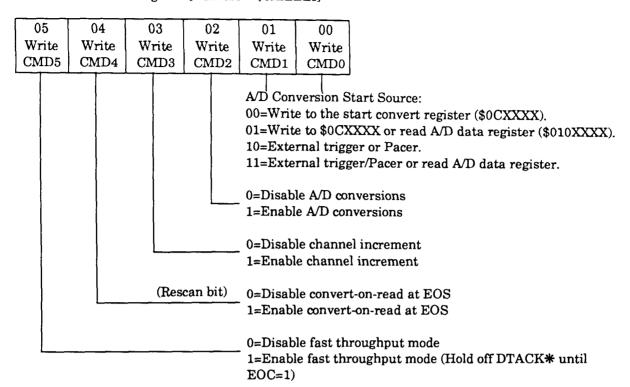

| 4.3.3   | A/D Command/Status Mode Register                         | 4-12<br>1-19  |

| 4.3.3.1 | EOS and EOC Status Bits                                  | 4.19          |

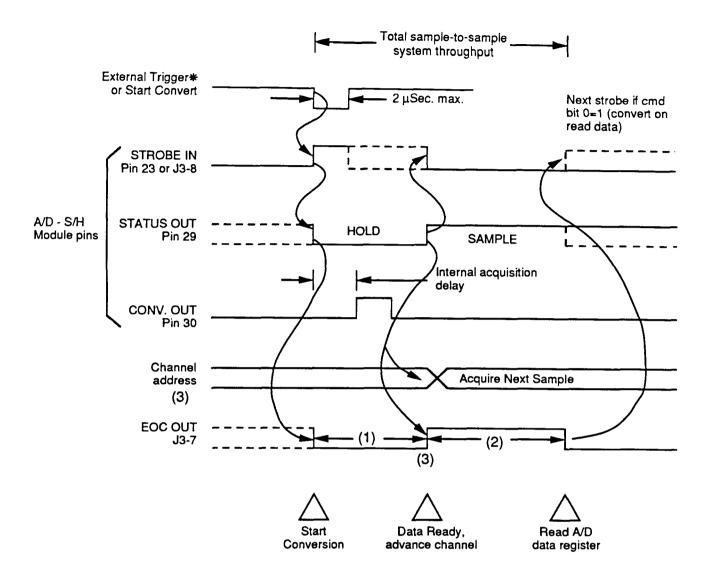

| 4.3.4   | A/D Conversion Start Methods                             | 4-13          |

| 4.3.5   | A/D Data Transfer Methods                                | 4-15          |

|         |                                                          | 1 10          |

| Section | 5 - Programming the Executive                            |               |

| 5.0     | Introduction                                             | 5-1           |

| 5.2     | Application Function Blocks                              | 5-1           |

| 5.3     | Application Function Block Subroutines                   | 5-3           |

| 5.4     | Function Block Execution                                 | 5-4           |

| 5.5     | Function Command Sequences                               |               |

| 5.6     | Command Start-up Procedure                               | 5-5           |

| 5.7     | Application Function Block Syntax                        | 5-6           |

| 5.8     | Application Function Block and Function Command Example  | 5-7           |

| 5.9     | DPR Executive Subroutines                                | 5-7           |

| 5.9.1   | A/D Conversion Start Subroutines                         |               |

| 5.9.2   | Destination Buffers                                      | 5-9           |

| 5.9.3   | Host Data Transfers Synchronization                      | 5-10          |

| 5.10    | Subroutine List                                          | 5-11          |

| 5.10.1  | Define Buffers and Host Synchronization                  | 5-13          |

| 5.10.2  | A/D Channel Address Register and Timer Initialization    | 5-15          |

| 5.10.3  | A/D Standard Scan Start Routines                         | 5-15          |

| 5.10.4  | A/D Pacer Timer/Data Read Scan Start Routines            | 5-16          |

| 5.10.5  | A/D Trigger/Data Read Scan Start Routines                | 5-16          |

| 5.10.6  | A/D Scan Start with Pacer Timer Settling Delay           | 5-17          |

| 5.10.7  | A/D Scan Start with External Trigger Settling Delay      | 5-17          |

| 5.10.8  | A/D Standard Single Channel Start Routines               | 5-18          |

| 5.10.9  | A/D Pacer Timer/Data Read Single Channel Start Routines  | 5-18          |

| 5.10.10 | A/D Trigger/Data Read Single Channel Start Routines      | 5-19          |

| 5.10.11 | A/D Single Channel Start with Pacer Timer Settling Delay | 5-19          |

|         | A/D Single Channel Trigger Start                         | 5-19          |

| 5.11    | Command/Status Control Word Definitions                  |               |

| 5.12    | DPR ACKnowledge Command Protocol                         |               |

| 5.13    | MC68901 Peripheral Controller Local Addresses            |               |

| 5.14    | Local RAM Reserved Locations                             |               |

| 5.15    | Interrupt Vector Assignments                             | .5-31         |

| 5.16    | Stack Definition when at the Monitor Level               | .ე-პ2<br>იი გ |

| 5.17    | Local CPU Wait States                                    | . 5-32        |

# Section 6 - Local Programming

| 6.0         | Introduction                                          | 6.1  |

|-------------|-------------------------------------------------------|------|

| 6.1         | Local Subroutines                                     | C 1  |

| 6.1.0       | Serial Port Local Subroutines                         | 0-1  |

| 6.1.1       | Arithmetic Local Subroutines                          | 6-2  |

| 6.1.2       | Breakpoint Timing                                     | ნ-პ  |

| 6.1.3       | VMEbus Interrupt Operation                            | b-8  |

| 6.2         | Local A/D Data Buffer Control                         | 6-8  |

| 6.3         | Thermocouple Temperature Measurement                  | 6-10 |

| 6.3.1       | Input Channels                                        | 6-10 |

| 6.3.2       | Cold Junction Compensation                            | 6-10 |

| 6.3.3       | Channel Addressing                                    | 6-11 |

| 6.3.4       | Gain and Input Ranges                                 | 6-11 |

| 6.3.5       | Thermocouple Arithmetic Operations                    | 6-12 |

| 0.5.5       | Thermocouple Artifiliede Operations                   | 6-13 |

| Sectio      | on 7 - External Triggering                            |      |

| 7.0         | External Triggering                                   | 7-1  |

| 7.1         | Trigger Inputs                                        | 7-1  |

| 7.2         | Trigger Programming                                   |      |

| 7.3         | Pacer Clock Triggering                                |      |

| 7.4         | Trigger Rates                                         | 7-2  |

| 7.5         | Contiguous Channel Mapping for DVME-64X MUX Expanders | 7-3  |

| 7.6         | DVME-601 EXEC ON/OFF Timing from the DPR              | 7-4  |

| 7.7         | Logical DPR Addressing                                | 7-4  |

| <b>7</b> .8 | Quiet Mode Conversion                                 | 7-5  |

| Sectio      | on 8 - Theory of Operation                            |      |

| 8.0         | Repair and Servicing                                  | 8-1  |

| 8.1         | Bus Interface Logic                                   | 8-1  |

| 8.2         | Dual Port RAM and Arbitration Logic                   |      |

| 8.3         | MC68010 CPU and Memory Section                        |      |

| 8.4         | MC68901 Multifunction Peripheral Section              |      |

| 8.5         | Command Register and Address Decode Logic             | 8-2  |

| 8.6         | A/D Converter Section                                 | 8-2  |

| 0.0         | AD Converses Decelor                                  |      |

| Section     | on 9 - A/D Section Calibration                        |      |

| 9.0         | Introduction                                          | 9-1  |

| 9.1         | Equipment Required                                    | 9-1  |

| 9.2         | Board Setup                                           | 9-1  |

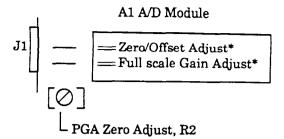

| 9.3         | Instrumentation Amplifier Zero Adjust                 | 9-1  |

| 9.4         | A/D Adjustments                                       | 9-1  |

| 9.5         | Zero/Offset Adjust                                    | 9-3  |

| 9.6         | A/D Gain Adjustment                                   | 9-3  |

Important: For channel expansion inputs, connect the solder gaps. See Section 3.2

# GENERAL INFORMATION

#### 1.0 Introduction

## 1.0.1 Scope of This Manual

Thank you for your interest in DATEL's DVME-601 A/D coprocessor board. This manual contains complete information to configure, install, program and use the DVME-601. Diagnostic, theory of operation and calibration information is included as well as a full set of schematic and assembly drawings. For customers, DATEL also offers the source code for the Monitor/Executive EPROM firmware on separate media.

Preliminary trouble-shooting may be accomplished with this manual but extensive component level repairs should be referred to DATEL. Users with critical downtime applications should consider stocking whole spare boards.

#### 1.0.2 Who This Manual Is Intended For

DVME-601 users should be familiar with all aspects of developing a high performance data acquisition application. This includes selecting, installing and connecting sensors to the DVME-601, complete operation of the host VME computer, and software programming. The user should clearly understand the arithmetic procedures for handling A/D data, possible error sources (both hardware and software) and system timing required. Some knowledge of digital logic, microprocessors and precision analog circuits will prove helpful. Although the DVME-601 contains extensive programs in its EPROM memory, the user must still write computer programs in the host to control the DVME-601 and transfer A/D data blocks to system memory. If any local DVME-601 programs are to be developed, the user must be proficient in 68000/68010 assembly language even if a high level language is used. The user must also be skilled at using the program development tools and operating system of the host computer. Software examples given in this manual assume that the user understands 68010 programming.

#### 1.0.3 Related Information

Besides this manual, the following information should be consulted:

DATEL DVME-601 Data Sheet

DATEL DVME-601 EPROM Source Code and Related Programs (available on floppy disks and other media for various computers - contact the home office. These disks contain valuable program examples).

MOTOROLA M68000 Microprocessor Programmer's Reference Manual (Contact Prentice-Hall, Inc., Englewood Cliffs, NJ, USA, 07632 for the latest edition. This includes 68010 information.)

Users should also have the full set of hardware, program development and operating system documentation available for their host VME computer.

#### 1.0.4 Equipment Requirements

Besides the DVME-601 board, you will need the following:

An analog signal source such as DATEL's DVC-8500A Voltage Calibrator or a group of input sensors.

[Optional]: A second asynchronous ASCII terminal/keyboard (RS-232-C, 9600 baud, 8 data, no parity, 1 stop) is very desirable for calibration and initial testing, even if you do not intend to write local DVME-601 programs. It will connect to the DVME-601 front panel. This terminal is in addition to your host terminal. An RS-232-C crossover cable will be needed. This terminal is mandatory for debugging local DVME-601 programs.

[Optional]: A VMEbus extender board.

[Optional]: Various probes and test equipment such as a pulse generator to simulate external A/D start triggers.

[Optional]: If you write local programs and load them into the DVME-601's EPROM's, you will need an EPROM programmer and cabling which can accept 27C256 or 27C512 EPROM's. You may also want an ultraviolet erasing lamp. A communication or copy program is required in your host to transfer your DVME-601 S2 records to the EPROM programmer.

#### 1.0.5 Implementation Procedure

The general outline for implementing an application using the DVME-601 is shown below. This procedure will be expanded throughout the rest of this manual.

- 1. Study your host computer and its documentation to decide how the DVME-601 will be integrated (board slot, memory addressing, interrupts, Operating System interface, etc.).

- 2. Configure the on-board hardware (jumpers, PGA gain, etc.) if it should be different from the factory settings.

- 3. Install the board and connect the optional terminal. Verify that your host operates normally after the installation. Do preliminary testing and command familiarization. Connect analog input signals.

- 4. Develop and debug your software for both the host and optional local programs. Reprogram the EPROM if desired.

- 5. Document your application so that it can be maintained and enhanced and for application questions.

#### 1.1 Description

Designed for today's VME environment of real-time operating systems and busy host processors, DATEL's DVME-601 is a high performance A/D data acquisition system integrated with a local 68010-based single-board microcomputer. The DVME-601 smart A/D board performs simultaneous analog data collection while concurrent VME host processing continues. Unlike dumb A/D boards, the DVME-601 will automatically collect scans without delaying other host software tasks. When A/D data is ready, the 601 can interrupt the VME host so that the host can memory transfer previous scans without stopping collection of the next scan.

Typical applications for the DVME-601 include high speed process control loops, analytical instruments, research laboratories, vehicular data recorders, ATE equipment and communications testers. The block-oriented, interrupt-controlled, memory transfers of A/D scans to the host are particularly suited to Digital Signal Processing applications in acoustics, sonar, high speed mapping, seismology, medical imaging, graphics, array processing, FFT's and waveform analysis. Using the single-channel fast-throughput mode and 2 microsecond converter, true 12 bit speeds over 250,000 samples per second to memory are available (single-channel, gain=1).

The data acquisition section includes an analog input multiplexer with 16S/8D local channels expandable up to 256 total channels using DATEL's slave MUX boards. An Instrumentation Amplifier is included which may be resistor-programmed by the user up to a gain of 1000. A choice of pluggable A/D Converter modules is offered on five different models. Resolution from 12 to 16 bits is available with 12-bit conversion speeds down to 2 microseconds.

A/D conversion may be started by external trigger, internal programmable timer, by local programs and indirectly by host command. All of these start modes are managed by on-board EPROM firmware. A DC/DC converter supplies low-noise regulated power to the data acquisition section.

The primary interface between the 601 and its VME host is a 64 Kb dual ported Random Access Memory (DPR). The DPR is used for commands, subroutines and parameters, control/status bits, A/D data blocks, optional downloads of user programs, and bidirectional interrupts between the 601 and the host. The maskable interrupt to the VMEbus normally occurs after A/D scanning but may also be commanded from a local user program.

Executive firmware included in the EPROM offers many ways to manage the DPR including swapped buffer ("ping-ponged") A/D scan transfers while the host reads the alternate buffer. The user may run the 601 either in the "no-programming" mode or may load and execute his own programs. The no-program mode uses fast A/D routines supplied in the EPROM. The firmware also includes a serial port Monitor to develop optional user programs.

The power and flexibility of the 601 can be enhanced with user-written software. As a high performance, general purpose microcomputer, the DVME-601 is ideal for automatic A/D data collection and arithmetic preprocessing of A/D data before sending it to the host. By transferring preprocessed results rather than raw data, total system performance can be increased while the host continues with disk, display or control activities. Programs may be developed in the host, saved on disk, then downloaded to local RAM via the DPR or serial port. The pluggable EPROM may be reprogrammed by the user or by DATEL under special order. Any language may be used such as Assembly, BASIC, FORTRAN or C if it can be compiled to 68010 code.

The local microcomputer consists of an 8 MHz MC68010 microprocessor, 64 Kb of pluggable EPROM (socketed to 128 Kb), 64 Kb of DPR and 64 Kb of private RAM. Total local storage of A/D data may approach 60,000 samples using the DPR plus private RAM if no other program is using RAM space.

A Multifunction I/O Peripheral using a programmable 68901 controller is also included offering an interrupt controller, an RS-232-C serial port, 4 timer/counters, and 5 I/O bits. Some of the timers and the serial port are used by the Monitor/Exec firmware but may be reprogrammed by the user including external interrupts. A second RS-232-C serial port is available using a software UART and the I/O bits. A front panel green LED lamp is illuminated to confirm power-up selftest and may be programmed by the user for alarms, etc.

Using the serial port, a 16 MHz clock source and a +5V dc power supply, it is even possible to operate the DVME-601 in stand-alone mode, not connected to the VMEbus. Commands and A/D data pass through the port up to 19.2 kilobaud with user-written programs.

The board uses +5V dc at 3 Amps and  $\pm 12V$  dc at 5 mA (typical) from the VMEbus. Connections are made only to P1 (P2 is not used to assure compatibility with most hosts). Data transfer is 16 bits wide. The DVME-601 is a D16 A24 slave board using 24 address lines and 6 address modifier lines. The board occupies 64 Kb of host memory. A single interrupt to the host asserts a programmable interrupt vector. Three front panel D connectors are provided for local analog inputs, analog slave-MUX channel expansion and for the Serial/Parallel/Timer I/O.

The DVME-601 is supplied on a 9.19"W x 6.3"D x 0.6"H (233,5 x 160 x 15,2 mm) 6U board. It includes a comprehensive User's Manual with programming information. Access to the EPROM source code in several formats is available to customers on special request.

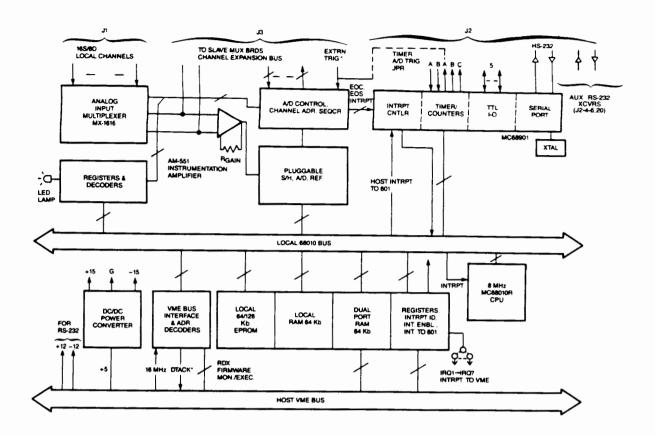

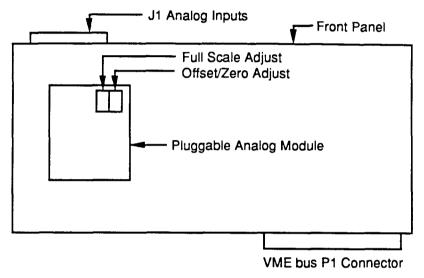

Figure 1.1 DVME-601 Block Diagram

## 1.2 DVME-601 Specifications

Specifications are typical @ +25 °C, gain = 1, unless noted.

## **Data Acquisition Section**

Number of On-board Channels 16 single-ended or 8 differential inputs, non-isolated, jumper selectable.

Analog Channel Expansion Up to 256 total channels, local and remote using DATEL's channel expansion bus and slave Multiplexer Boards. Chan-

nels may be mixed single-ended or differential on slave MUX

boards. (10 slave MUX boards maximum)

Input Voltage Range  $\pm 10$  Volts full scale. ( $\pm 5$ V, 0 to +10V, and 0 to +5V may be

jumpered or special-ordered. See Figure 2.6).

Common Mode Voltage Range ±10V, maximum, non-isolated.

Common Mode Rejection 80 dB, dc to 60 Hz,  $CMV = \pm 10V$ , with 1 Kilohm source

unbalance, gain = 1.

Input Bias Current ±200 pA

Overvoltage Protection

±30V dc, maximum sustained

Input Impedance

Power on: 1000 Megohms, differential or to ground.

Power off: 1.5 Kilohms

A/D Output Coding

Left-justified bipolar 2's complement, jumperable to bipolar offset binary or unipolar straight binary for DVME-601A. Other models are bipolar 2's complement or offset binary.

Instrumentation Amplifier Type and Gain Range

AM-551 supplied as gain = 1.

May be resistor-programmed by user up to gain = 1000 with

increased settling delay.

Instrumentation Amplifier Settling Delay (gain=1)

3 microseconds to 0.01% of FSR

(The Inst. Ampl. may be by passed for faster single-ended

throughput.)

Adjustments

Inst. Ampl.offset, A/D offset and A/D gain.

A/D-S/H Resolution and Conversion Period Options: (Uses pluggable modules)

| Model     | Resolution | Convert time  | Thruput to RAM* |

|-----------|------------|---------------|-----------------|

| DVME-601A | 12 Bits    | 20 microsec.  | 40 KHz          |

| DVME-601B | 12 Bits    | 4 microsec.   | 114 KHz         |

| DVME-601C | 16 Bits    | 35 microsec.  | 25 KHz          |

| DVME-601D | 16 Bits    | 400 millisec. | 2.5 Hz          |

| DVME-601E | 12 Bits    | 2 microsec.   | see notes       |

| DVME-601F | 14 Bits    | 4 microsec.   | 100 KHz         |

<sup>\*</sup>The typical throughput rate is an aggregate time within a multichannel scan and does not include subroutine setup time. The rate includes times for channel sequencing, MUX, Inst. Ampl., S/H acquisition/settling, A/D conversion, and 68010 software times. The polled-EOC STSNSC subroutine is used, triggering A/D conversion on each data read. Higher single-channel speed is available using the "fast-throughput" mode (delayed DTACK\*). The DVME-601E offers 300 KHz in a long burst to local RAM, single channel, gain=1. In multichannel, all modes require at least 6 microseconds (gain = 1) from channel sequencing to A/D start plus the A/D conversion time. Data transfer time may overlap A/D conversion.

## System Performance

| Specification                                          | 601A       | 601B,E     | A/D type<br>601C | 601D       | 601F       |

|--------------------------------------------------------|------------|------------|------------------|------------|------------|

|                                                        | 12 bit,    | 12 bit,    | 16 bit,          | 16 bit,    | 14 bit,    |

|                                                        | 20 μS      | 2 or 4 μS  | 35 μS            | 400 mS     | 4 μS       |

| Accuracy, min.                                         | 0.025%     | 0.05%      | 0.01%            | 0.0063%    | 0.01%      |

|                                                        | of FSR     | of FSR     | of FSR           | of FSR     | of FSR     |

| Nonlinearity, max. Zero tempco, max. Gain tempco, max. | 1/2 LSB    | 1/2 LSB    | 2 LSB            | 2 LSB      | 2 LSB      |

|                                                        | ±20 ppm/°C | ±20 ppm/°C | ±20 ppm/°C       | ±10 ppm/°C | ±15 ppm/°C |

|                                                        | ±20 ppm/°C | ±20 ppm/°C | ±20 ppm/°C       | ±10 ppm/°C | ±15 ppm/°C |

External A/D Start Trigger

Negative-going TTL input with 4.7 Kilohm pullup to +5V.

Pulse width 100 nS min., 2 microsec. max.

Local Pacer Clock

Software programmable to cause A/D Start Timer either an

A/D scan start or a single conversion.

Pacer Clock Interval Range

3.255 microseconds to 41.667 mS (supported in firmware) us-

ing one timer. Up to 3.03 hrs. using 3 cascaded timers.

Local Microcomputer

CPU Type and Clock Speed

MC68010R8, 8 MHz (CPU clock is derived from 16 MHz bus

SYSCLOCK).

Local data bus width

16 Bits

Local Read/Write Memory

64 Kilobytes static RAM (no VMEbus access)

Local Read-only Memory

UV-erasable EPROM, 64 Kilobytes supplied as two 27C256's

but is socketed for two 27C512's totalling 128 Kb. The

EPROM contains Monitor/Executive firmware.

Dual-ported Read/Write Memory (VMEbus and local access)

64 Kilobytes

Front Panel LED Lamp

Green LED lamp is lit if power-up local CPU selftest succeeds. Thereafter, the lamp may be programmed by user

software for alarms, etc.

Peripheral I/O Controller

Controller Type

MC68901 multifunction peripheral, crystal-controlled,

2.4576 MHz, user-programmed.

Interrupts

Local Hardware Interrupts

A/D End of Conversion, to 68010 CPU (Maskable) A/D End

of Scan, VMEbus host command request

Local Software Interrupts

Any timer count reached or (Programmable) I/O bits 0-4.

Digital I/O

Number of I/O Lines

5 lines, individually programmable as inputs or outputs or

interrupts.

Logic Levels

TTL levels, 1 load max. with 10 Kilohm pullups to +5V.

Timer/Counters

**Number of Timers**

4 8-bit timers with prescale up to divide-by-200.

Timer Outputs

3 outputs, (Timers A,B,C), 1 TTL load max. The Timer D is

the USART baud clock but may be reprogrammed.

Timer/Counter Inputs

2 inputs, TTL levels with 10 Kilohm pullups to +5V.

**Serial Port**

Number of Serial Ports

1 USART, full duplex, RS-232-C levels, DTE pinout. Aux.

RS-232-C I/O may be configured.

RS-232-C Handshakes

DTR, DSR, RTS, CTS program- by the user. (See J2 pinout).

Modes

Synchronous or asynchronous.

Number of Stop Bits

0, 1, 1.5, 2

Number of Data Bits

5, 6, 7, 8

Parity

Odd, even, none for receiver. Transmitter is user-coded.

**Baud Rates**

Up to 19.2 Kilobaud.

[EPROM Monitor firmware uses the serial port and timer D at 9600 baud, 8 data, no parity, 1 stop. A 4800-baud software UART is formed with I/O bit 0 for optional serial S record downloads. Firmware also uses Timer A as an A/D start clock. All functions may be reprogrammed by the user.]

#### **VMEbus Interface**

Standards Compliance

IEEE P1014/D1.0

Data Bus Width

16 Bits

Address Bus

A24 D16 slave, 24 address lines, A23 - A01, plus 6 address

modifiers, jumper selected.

Address Modifier Codes

39h, 3Ah, 3Dh, 3Eh jumperable. (see jumper information)

Architecture

Dual-ported 64 Kb block mapped on 64 Kb boundaries. One

address (force interrupt to 601) is write-only. All others are

Read/Write. (See memory map).

VME Bus Interrupter

1 line, jumper-selectable IRQ1\* thru IRQ7\*. Asserts one interrupt ID code which is programmable from the host. Interrupt is generated by a 601 local register write and is

maskable by a host-writable register.

Data Transfer

16 bits using P1. Generates DTACK\* derived from 16 MHz

bus clock.

Connectors

VMEbus, P1

96-pin male DIN connector. No P2 connector is used.

Local Analog Input, J1

25-pin DB-25S female on front panel.

Multifunction I/O

Peripheral (68901), J2

25-pin DB-25S female on front panel.

Analog Input Channel Expansion Bus, J3

25-pin DB-25S female on front panel, compatible to DATEL

DVME-64X series MUX boards.

Miscellaneous

Power Required

+5V dc  $\pm 5\%$  @ 3.0 Amps max. (DVME-601A) or 3.1 Amps max. (DVME-601B,C,D,E,F) and  $\pm 12$ V dc @ 10 mA max. from VMEbus. The 12V power is only required if the serial port is used. A local  $\pm 15$ V dc DC/DC converter is included

for linear circuits.

Operating Temperature

0 to +60 °C

Storage Temperature

-20 to +80 °C

Relative Humidity

10% to 90%, non-condensing.

**Outline Dimensions**

Double-height VME, 6U outline. 9.19" W x 6.3" D x 0.6" H,

(233,5 x 160 x 15,24 mm).

Weight

17 ounces (482 grams)

Allow 20 minutes warmup time for model DVME-601F.

# BOARD CONFIGURATION AND INSTALLATION

## 2.0 Determining Your Host Environment

Before installing the board in your host computer, you should consult your host documentation. Installation must not disrupt the normal operation of your host and must be compatible with its resources. If your development environment differs from the target application, you should be aware of the differences.

DVME-601 host compatibility involves two major areas:

## 2.0.1 Host Memory Map Compatibility

The 64 Kilobyte memory block occupied by the board must not conflict with other system memory. This has two consequences:

- 1. The board's 64 Kb dual port RAM cannot overlay or respond to the same address codes as Random Access Memory (RAM) or other memory-mapped peripherals in the host.

- 2. On host power up, many operating systems test for how much contiguous read/write memory there is, starting from low memory. If the DVME-601 is mapped adjacent to system RAM used by the operating system, memory location BASE + \$0FFFC will be detected as the top of contiguous RAM. This is because this location is actually a DVME-601 write-only memory-mapped hardware register and will be the first location which fails read/write memory testing by the host. Some operating systems attempt to place the machine stack just below this area, which would be located at the top of DPR. This conflicts with other DVME-601 hardware registers and the DPR command area.

Other operating systems may attempt to read memory size switches or PROM's set by the computer manufacturer. These should not be changed to accommodate the DVME-601.

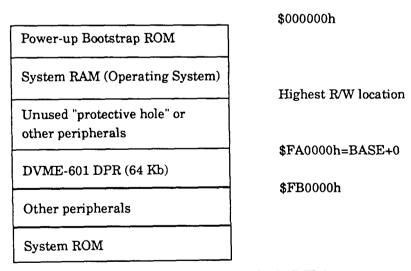

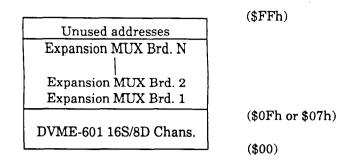

A recommended procedure is to locate the DVME-601's BASE address away from system RAM, separated by an area which will fail operating system memory testing. (This area should not have anything which responds to a memory read/write access). This "protective hole" will make your system memory map appear similar to figure 2.0. (Factory supplied addressing is shown). Positioning the DVME-601's BASE address relative to the host is done by setting the base address switches, discussed in the next section.

Default factory-jumpered BASE addressing is shown for the DVME-601.

Figure 2.0 Typical Simplified Host Memory Map

## 2.0.2 Host Interrupt Compatibility

The other compatibility area involves VMEbus interrupts. If you plan to make long multiple A/D scans which are asynchronous with other complex host activities, interrupts are a desirable way to periodically resynchronize the entire system and maintain system bandwidth. Interrupts require the following decisions:

- A. The Interrupt Request line to VMEbus (IRQ1 through IRQ7) must be jumpered. This determines interrupt priority. This is discussed in following sections.

- B. A vector address must be loaded by your host into the DVME-601's ID register (DPR location BASE + \$0FFFA) after host power-up. This address is used by the CPU (after 2 left shifts) to develop the interrupt service routine (ISR) address. The ISR is either an absolute address or an offset from the CPU's Vector Base Register.

- C. Programs are required in your host to respond to DVME-601 interrupts, process commands and transfer A/D data.

Your target application is likely to handle interrupts in one of two ways:

- A. If you are NOT using a multitasking Real Time Operating System (RTOS), the interrupt controller in your host must be loaded with a vector address pointing to code to handle interrupts from the DVME-601. Obviously you must also have developed such code and it must be resident in memory.

- B. If you ARE using an RTOS, interrupts are handled symbolically and you probably will not have to do low level interrupt controller programming. You must still write code to process DVME-601 commands and transfer data plus arbitrate with the RTOS. You will need to decide a priority for the DVME-601, how it communicates with other system tasks and how its status is managed. RTOS programming is beyond the scope of this manual.

Be aware that processing interrupts through an RTOS can take extra time because of overhead. With multiple random system interrupts, this delay is not always predictable or easy to measure. Unless interrupts are temporarily masked off during a long A/D memory fill, RTOS usage may not be suitable for very high bandwidth applications.

Most users will develop their DVME-601 application on a DOS-based development system. Target applications which execute out of PROM without a DOS may have many differences in memory mapping, interrupts, etc. Be aware of these differences in transferring from development to target environments.

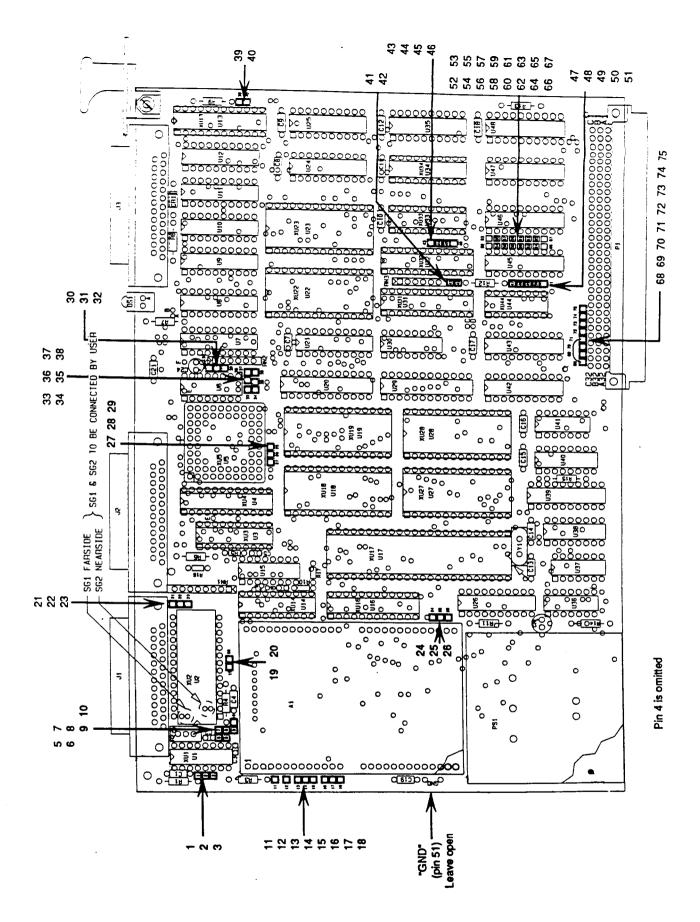

Figure 2.1 Assembly and Layout Diagram (Component Side) [Drawing D-15259]

#### 2.1 Base Address Selection

In the following sections, please refer to the Assembly Diagram, Figure 2.1, to locate jumpers and other hardware. Position the board with the VMEbus connector, P1 at the lower right. Most of the factory jumpering will be correct for many applications. However, you should carefully check all jumpering before installing the board. Removable plugs are used for some connections and soldered jumpers or wire wrap posts are used for others.

The DVME-601 may be configured to occupy a 64 kilobyte block in the memory space of the host CPU. Jumper plugs are provided to select the BASE (lowest) address of the memory block using VMEbus address lines A23 through A16. Address lines A15 and below are locally decoded on the DVME-601 to address the DPR. Wire wrap connections may be used if preferred. The jumpers are located between integrated circuits U45 and U46 in the lower right just above P1. Please refer to Figure 2.2.

An installed jumper decodes a logic 0 for its associated address line. If the jumper is omitted, a logic 1 results. The DVME-601 is shipped at a standard BASE address of \$FA0000 hexadecimal.

| ADDRESS LINE | JUMPER   |

|--------------|----------|

| ADR 23       | 66 to 67 |

| ADR 22       | 64 to 65 |

| ADR 21       | 62 to 63 |

| ADR 20       | 60 to 61 |

| ADR 19       | 58 to 59 |

| ADR 18       | 56 to 57 |

| ADR 17       | 54 to 55 |

| ADR 16       | 52 to 53 |

Jumper installed = 0, Jumper omitted = 1

Figure 2.2 BASE Address Jumpers

## 2.2 Address Modifier Selection

A jumper must be installed to select the desired Address Modifier code(s). The Address Modifier jumpers are located just to the left of the BASE address jumpers between U44 and U45. AM codes \$29 and \$2D are listed below but should not be used for the DVME-601. Codes \$3A and \$3E allow the host to fetch and execute instructions out of the DPR. Normally this mode would not be used but is possible if required. Note that the DVME-601 may always be accessed in Supervisory Mode. See Figure 2.3.

| Jumper | Responds to | Access description                     |

|--------|-------------|----------------------------------------|

| 47-48  | Code \$39   | Standard non-privileged data access    |

| [STD.] | Code \$3A   | Standard non-privileged program access |

|        | Code \$3D   | Standard supervisory data access       |

|        | Code \$3E   | Standard supervisory program access    |

| 47-49  | Code \$3D   | Standard supervisory data access       |

|        | Code \$3E   | Standard supervisory program access    |

| 47-50  | Code \$29   | Short non-privileged access            |

|        | Code \$2D   | Short supervisory access               |

| 47-51  | Code \$2D   | Short supervisory access               |

Figure 2.3 Address Modifier Jumpers

## 2.3 Interrupt Level Selection

The DVME-601 may generate interrupts to the VMEbus host system using interrupt levels 1-7. There are several sets of jumpers as shown in Figure 2.4. The interrupt request jumpers are located immediately above the P1 VMEbus connector. Other interrupt jumpers are between U44 and U45 and between U32 and U33. These IC's are just above P1. The desired interrupt level is selected by jumpers as follows:

| Interrupt | Install Jumpers   |       |       |       |  |  |

|-----------|-------------------|-------|-------|-------|--|--|

| Level     | BIRQ* Line Jumper | 43-44 | 45-46 | 41-42 |  |  |

| 1         | 68 to 69          | IN    | IN    | OUT   |  |  |

| 2         | 68 to 70          | IN    | OUT   | IN    |  |  |

| 3         | 68 to 71          | IN    | OUT   | OUT   |  |  |

| 4         | 68 to 72          | OUT   | IN    | IN    |  |  |

| 5         | 68 to 73          | OUT   | IN    | OUT   |  |  |

| 6         | 68 to 74          | OUT   | OUT   | IN    |  |  |

| 7         | 68 to 75          | OUT   | OUT   | OUT   |  |  |

Figure 2.4 VMEbus Interrupt Level Selection

## 2.4 A/D Converter Jumpering

The A/D Converter must be jumpered for single-ended or differential inputs, input voltage range, and output data coding. In addition, the AM-551 Instrumentation Amplifier, U1, may be bypassed. This offers slightly faster settling times and can only be used with single-ended inputs. Differential inputs always require the Instrumentation Amplifier.

Single-ended inputs use channels 0 through 15. Differential inputs use channels 0 through 7. Most jumpers are adjacent to the Data Acquisition Section in the upper left. Jumpers 39 and 40 are on the upper far right board edge.

## 2.4.1 Single-Ended/Differential Inputs

IMPORTANT! Both single-ended configurations should REMOVE jumper 22-23. Otherwise -15V dc will be connected to the channel address generator and damage could result. The differential configuration should connect ONLY jumper 22-23 as shown. Users should study the schematic drawing, sheet 5, to understand all the connections.

Single-ended input: Install: 9-10, 19-20, 21-22

(No inst. ampl.) Remove: 1-2, 2-3, 5-6, 8-9, 39-40, 22-23

Single-ended input: Install: 1-2, 5-7, 8-9, 19-20, 21-22 (with inst. ampl.) Remove: 2-3, 5-6, 9-10, 22-23, 39-40

[factory standard]

Differential input: Install: 2-3, 5-7, 8-9, 22-23, 39-40 (with inst. ampl.) Remove: 1-2, 5-6, 9-10, 19-20, 21-22

The jumpers near the AM-551 PGA (U1) are difficult to see on the board. They are as follows:

To use any of the expansion slave MUX boards (DVME-64X series), the DVME-601 must be configured for local differential input by carefully cutting the 19-20 jumper with miniature cutters or removing the 19-20 plug if it is installed. Local single-ended inputs on the 601 are not allowed if slave MUX boards are connected because the expansion bus is inherently differential. Single-ended input on the slave MUX board is allowed however.

#### 2.4.2 Instrumentation Amplifier Gain Selection

The AM-551 Instrumentation Amplifier U1, is normally supplied with a gain of one. However the gain may be increased up to 1000 by changing a jumper and adding a gain resistor. The resistor is normally omitted and is installed in location R1 in the extreme upper left of the board.

There are several practical consequences of increasing the gain. The gain is related to the temperature coefficient of the gain resistor. Therefore R1 should be a high quality, low-TC metal film type. At higher gains, the AM-551 requires additional settling time and has somewhat lower small signal bandwidth. Refer to Figure 2.5. For values between those shown, the user should interpolate. Consult DATEL'S AM-551 data sheet for more information.

| Total<br>Gain | Settling time, 20V<br>output to 0.01% | Small signal<br>bandwidth, -3 dB |

|---------------|---------------------------------------|----------------------------------|

| 1             | 2 μS, typ.                            | 400 KHz typ.                     |

| 10            | 4.6 μS, typ.                          | 150 KHz typ.                     |

| 100           | 20 μS, typ.                           | 100 KHz typ.                     |

| 1000          | 200 μS, typ.                          | 40 KHz typ.                      |

Figure 2.5 Instrumentation Amplifier Characteristics

Gain is selected for both the input and output stages of the AM-551. The input stage may be continuously varied up to gain=100 by selecting R1. The value for R1 is determined by a formula. The output gain is either 1 or 10 by changing a jumper. The total AM-551 gain is the input gain times the output gain.

Gain selection is accomplished in two stages. The input stage gain (G1) is selected by R1 and is expressed as follows:

$$R1 = 20 \text{ Kilohms/}(G1 - 1)$$

The output stage gain (G2) is selected by jumper. For G2 = 1, install jumper 5 to 7. For G2 = 10, install jumper 5 to 6.

A single gain resistor location is provided. Therefore, most standard value resistors may not provide exactly the gain required. To calibrate for higher gains, these are some possible alternatives:

- 1. The gain may be initially set with a precision standard value metal film resistor of slightly higher value (lower gain) than is required. The final gain is determined empirically with a voltage calibrator and a high-value trim resistor which parallels the precision resistor. The two resistors are soldered closely together and installed at the R1 location.

- 2. If a single standard value resistor provides gain that is very close to the desired amount, the gain control on the A/D converter module may be used to adjust the final value. Refer to the A/D calibration procedure since this may also alter the zero or offset calibration.

- 3. A single precision resistor may be used that provides approximately the correct value. Final gain is then done in software by multiplying all raw binary data values by a calibration constant. The arithmetic may be done locally on the DVME-601 before sending data to the host.

If two analog input channels are dedicated to ground and full scale reference inputs, the constant may be calibrated automatically and continuously with every Nth scan. Using both ground and full scale references, a first order  $Y = MX \pm B$  equation will offer autozeroing as well. Thus each DVME-601 will be autocalibrating. There is of course a speed penalty for the software autocalibration but it may be combined with sensor linearization programming which was to be performed anyway.

Finally, you should be aware that total system gain must also consider the A/D converter input range, discussed in the next section. Using a lower A/D input range changes the bit weighting (the millivolt value of each output data count) just as effectively as changing the AM-551 gain.

## 2.4.3 A/D Input Range and Output Data Coding Selection

For many applications, the standard A/D input ranges available on the DVME-601 will be sufficient and extra gain will not be required in the Instrumentation Amplifier. The DVME-601A is supplied with up to four user-selected input ranges. Two ranges are unipolar and two are bipolar. The DVME-601E has a bipolar and unipolar range. The DVME-601B-U and -601C-U are fixed as unipolar and are available under special order.

Bipolar ranges use one data bit for polarity indication whereas unipolar ranges do not have a polarity bit. A 12-bit A/D converter may be considered either 12 unipolar data bits or 11 bipolar data bits and a sign bit.

A/D models and input range options are shown in Figure 2.6. Jumpers to select these ranges are shown in Figures 2.7 and 2.7a. Range jumpers are along the extreme left edge of the board outside the A/D converter module. A/D data output coding may be either unipolar straight binary, bipolar offset binary or bipolar two's complement.

A/D output coding is shown in Figure 2.8. Output coding jumpers are along the lower right corner of the A/D converter. The jumper inverts the converter's most significant data bit. Refer to the calibration section for information on coding and input ranges.

If possible, group all inputs together as sequential channels and avoid scanning through unused inputs. Scanning through open inputs will not delay scanning but may degrade settling performance on the next channel. If you must scan through unused inputs, consider grounding them or connect a high value input resistor to ground (say 50 Kilohms) on each unconnected input to prevent amplifier saturation. Unterminated inputs may display small stray MUX feed through and crosstalk signals.

| Board Type                 | DVME-601A             | DVM      | E-601B       | DVME-601C                  | DVME-601D    | DVM      | E-601E       | DVME-601F    |

|----------------------------|-----------------------|----------|--------------|----------------------------|--------------|----------|--------------|--------------|

| A/D Module<br>Type         | ADC-12/20             | ADC-12/2 | ADC-12/2A    | ADC-16/35                  | ADC-16/400K  | ADC-12/2 | ADC-14/2A    | ADC-14/2     |

| Full Scale<br>Input Ranges |                       |          |              | Jumper S                   | elections    |          |              | 1            |

| 0 to +5V                   | 16-17, 13-18<br>14-15 | N/A      | N/A          | N/A                        | N/A          | N/A      | N/A          | N/A          |

| 0 to +10V                  | 16-17, 14-15          | 16-17    | 16-17        | (-U model)<br>16-17, 13-14 | N/A          | 16-17    | 16-17        | E2-E3        |

| ±5V                        | 16-17, 13-14          | N/A      | 16-17, 13-14 | 16-17, 13-14               | N/A          | N/A      | 16-17, 13-14 | E1-E2, E4-E5 |

| ±10V                       | 17-18, 13-14          | 13-14    | 17-18, 13-14 | 17-18, 13-14               | 17-18, 13-14 | 13-14    | 17-18, 13-14 | E1-E2        |

<sup>\*</sup>Note: DVME-601F models are supplied and specified as ±10 Volt full scale inputs but may be jumpered on the ADC-14/2 module only (not the 601 board) for 0 - 10V or ±5V. See the ADC-14/2 module drawing for details. On the DVME-601F jumpers, E1 - E5 are on the bottom surface of the A/D module. You must remove the A/D module to change the setting. Recent DVME-601B and -601E boards use ADC-12/2A modules.

Figure 2.6 A/D Input Ranges and Model Types

| A/D Output<br>Data Coding    | Polarity | Install<br>Jumper |

|------------------------------|----------|-------------------|

| Straight or<br>Offset Binary | Unipolar | 24 to 25          |

| Two's<br>Complement          | Bipolar  | 25 to 26          |

Figure 2.7 A/D Output Data Coding

# 2.4.4 DVME-601F Range Jumpers

| Range -1           | Internal<br>Jumper -2 | External<br>DVME-601F<br>Board Jumpers |

|--------------------|-----------------------|----------------------------------------|

| 0 to +10V          | E2-E3                 | Leave all board jumpers 17-21 open     |

| ±5V                | E1-E2<br>E4-E5        | Leave all board jumpers 17-21 open     |

| ±10V<br>(Standard) | E1-E2                 | Leave all board jumpers 17-21 open     |

#### Notes:

- 1. The 0 to 10V and ±5V ranges may experience increased noise. DATEL suggests averaging a sum of adjacent multiple data samples while locked on one channel.

- 2. The "E" jumpers are on the ADC-14/2 analog module. Unlike other -601 modules, range adjustments must be made on the module. To avoid damage, range jumpering should only be performed by a skilled person.

- 3. Differential mode is strongly recommended for 14-bit A/D operation.

- 4. The averaging technique in Note 1 may be performed very quickly in assembly language. First, reset the autoincrement bit in the command register (CMD3 = 0). Write the channel address, allow 6 microseconds minimum settling then start A/D conversions. Sum the data into the CPU accumulator, collecting a power-of-two number of samples. While locked on one channel, no settling time is required after the first conversion. Data may be read as fast as the EOC appears and fast throughput mode (CMD5 = 1) may be used to eliminate EOC polling. Now perform a root 2 right shift of the summed data, or simply use the larger sum.

Example: Sum 8 A/D samples and shift right 3 bits (LOG2 of 8=3). This avoids slow floating point averaging and can all be done in assembly language.

#### 2.5 Auxiliary RS-232-C Serial Port Jumpers

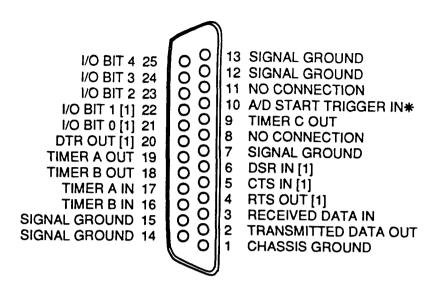

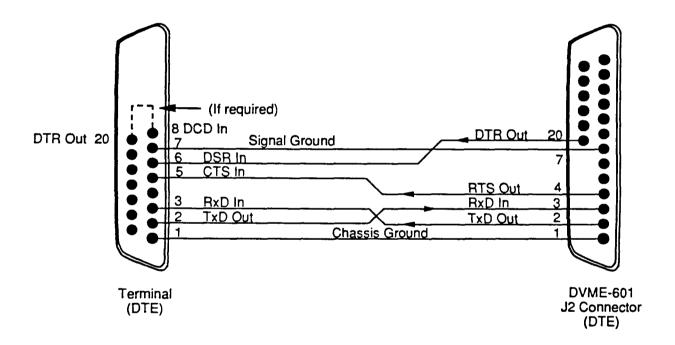

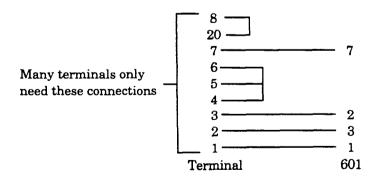

The J2 front panel connector serves several purposes. It is the primary connector for the 68901 peripheral controller but also accepts an external A/D trigger start input. The 68901 controller provides 5 TTL I/O bits, 2 timer/counter inputs, 3 timebase outputs and an RS-232-C serial port. This port is full duplex with synchronous and asynchronous character formats. It is pinned out as RS-232-C Data Terminal Equipment (DTE) as if it were a terminal. The discussion below assumes an understanding of RS-232-C specifications and serial data transmission. Please refer to the J2 connector pinout discussed in Section 3.

The serial port is the primary interface for the firmware Monitor. When connected to an external dumb AS-CII terminal, the Monitor is used to develop user programs, for A/D calibration and for diagnostics. After the Monitor is used, the J2 serial port may be reassigned by local user programs to other functions. When used as a serial port, the J2 connector and the 68901 controller offer a subset of the full RS-232-C interface. Most of the RS-232-C handshake lines are available depending on jumpering described below. The other 68901 controller connections on J2 for timer/counter/I-O are not part of the RS-232-C specification and should be reviewed before making connections to your Monitor terminal. This may be accommodated by wiring a special cable. Refer to Section 3 covering I/O connections.

Five of the general purpose I/O lines of the MC68901 controller are brought out on the J2 connnector as single load TTL logic levels. Two of these I/O bits, 0 and 1 on pins 21 and 22 may also be jumpered on the board to an unused RS-232-C line driver and to one of two unused RS-232-C receivers. These spare RS-232-C devices connect to J2 in the proper locations to act as RS-232-C handshakes for the 68901 serial port. They may also be programmed as a second serial port using a software UART.

Jumpering for the spare RS-232-C output is shown in Figure 2.9. The two spare RS-232-C inputs are jumpered according to Figure 2.10.

When these jumper connections are made, the raw TTL levels for I/O bits 0 and 1 will still be available on the J2 connector in addition to the RS-232-C levels. Be careful if you make connection to the I/O bits to preserve operation of the RS-232-C devices. Please refer to the DVME-601 Schematic Diagram, drawing number D-15260, sheet 4.

| Jumper        | RTS Output<br>(J2 pin 4)           |

|---------------|------------------------------------|

| 31 - 32       | Always true if power is on.        |

| 30 - 31       | Programmed by I/O bit 1 as output. |

| (use for aux. |                                    |

| ser. output)  |                                    |

Figure 2.9 Spare RS-232-C Output

| Jumper  | Input source to I/O bit 0 |  |

|---------|---------------------------|--|

| 37 - 38 | From CTS, J2 pin 5        |  |

| 36 - 37 | From DSR, J2 pin 6        |  |

Figure 2.10 Spare RS-232-C Inputs

#### 2.5.1 RS-232-C Serial Port Handshakes

The four standard RS-232-C handshakes (CTS, DSR, DTR, and RTS) connect to transceivers on the DVME-601. The Data Terminal Ready output (DTR) is always true at J2 pin 20 when power is on. The Request To Send output (RTS) at J2 pin 4 may be jumpered always true or may be software programmed by output bit 1. Most terminals connected to J2 will require these lines to be asserted.

Either (but not both) of the Clear To Send (CTS) or Data Set Ready (DSR) inputs at J2 pins 5 and 6 respectively may be jumpered to bit 0. User software would program this bit as an input. The 68901 controller has no internal CTS or DSR handshake logic to stop transmission when an external DCE device requests a halt. Using them as data flow control handshakes would require polling I/O bit 0 by a user program. Bit 0 may also be programmed as a local interrupt to avoid polling.

#### 2.5.2 RS-232-C Auxiliary Software Serial Port

The RS-232-C spare transceivers may also be programmed as a second software serial port. Serial input data is connected to either J2 pin 5 or 6. Software UART routines in the firmware use the auxiliary serial input as an S2-record downloader. The input defaults to 4800 baud, 8 data, no parity, 1 stop bit, asynchronous format.

The input allows the user to download S2-record programs from the host or an external development system. This is an alternative software channel to downloading through the DPR. It has the advantage that it is immediately compatible with most serial-loading development systems and does not require the user to write a DPR downloader right away. When using the downloader, both the controlling Monitor terminal and the download serial input must be connected. There is no hardware handshaking on the auxiliary serial port unless the user wanted to program the auxiliary RS-232-C output.

The RS-232-C output may be user-programmed by controlling I/O bit 1 on J2 pin 4. To form a serial output, a software output UART subroutine is provided in EPROM. The local program can call the subroutine.

#### 2.6 Analog and Digital Ground Connection

The analog and digital grounds are connected together inside the S/H-A/D module where they produce the highest data quality. The digital/power ground is also connected to the host system ground through the VMEbus backplane ground. The host may ultimately connect power ground to earth (chassis) ground through the AC third prong. Or the chassis may remain fully transformer isolated from earth ground. You should fully understand all implications of these ground connections to avoid large ground loop currents flowing through your input transducers or possible damage to the DVME-601.

In your complete application circuit, there must one and only one connection between the analog and digital/power ground systems (i.e., the connection inside the module). Using two or more parallel ground connections may introduce ground loop errors. The mistake commonly made is to ground the sensor shields to earth ground remotely out at the sensor while the shields are also connected to analog ground. This creates a large, single-turn transformer called a ground loop. The amount of noise current collected by this loop is proportional to the noise fields and the loop area. A fundamental rule is that ground shields should carry no current (including induced ground loop current).

CAUTION: The DVME-601 on-board channels are not isolated and can be damaged by excessive common mode voltages. If your application requires galvanic isolation between the two ground systems, consider using the DVME-643 slave isolated MUX board to connect all inputs. Contact DATEL if you need assistance.

#### 2.7 EPROM Memory Address Jumpers

The DVME-601 is supplied with 64 kilobytes of EPROM memory containing the Monitor and Executive firmware. This is provided in two type 27C256 EPROM's at U18 and U19 arranged in 16-bit word addressing. Please refer to the schematic drawing, D-15260, sheet 3.

Users with special program requirements may wish to consider larger EPROM's up to 128 Kb maximum. To configure 128 Kb of memory, address jumpers must be changed and new EPROM's will be required. Two type 27C512 devices should be installed at U18 and U19. The new EPROM's must be programmed properly before use. The installation should only be considered by a user skilled at electronic assembly. The reprogramming is discussed in a later section.

The DVME-601 will also accept lower cost 2764 and 27C128 EPROM's if required. Jumpering for all EPROM sizes is shown in Figure 2.11 below. The jumpers are adjacent to the 68010 microprocessor U5 in the top center of the board. Alternate EPROM sizes are available from DATEL under special order.

| Total<br>EPROM<br>memory | U18 & U19<br>device types | Install jumpers |  |

|--------------------------|---------------------------|-----------------|--|

| 16 Kb                    | (2) 2764/C64              | 34-35, 27-28    |  |

| 32 Kb                    | (2) 27C128                | 34-35, 27-28    |  |

| 64 Kb                    | (2) 27C256<br>[supplied]  | 33-34, 27-28    |  |

| 128 Kb                   | (2) 27C512                | 33-34, 28-29    |  |

Figure 2.11 EPROM Address Jumpers

#### 2.8 Board Installation

All DVME-601 jumpers should now be properly installed. Confirm that your host and its operating system function normally. Shut off host power.

Consult your host documentation to determine the proper board slot. The DVME-601 preserves the VMEbus Interrupt Acknowledge and Bus Grant chain. The board should be positioned in the next free board slot away from the host CPU board. If you must leave empty slots between the DVME-601 and the other system boards, be sure backplane IACK jumpers are in place for the empty slots. IACK jumpers should be out for the slot used by the DVME-601 if you want interrupts. Rearrange the sequence of boards if you want to vary the hardware priority of DVME-601 interrupts. Higher priority boards are nearer to the CPU board. The DVME-601 also includes board connections to daisy-chain bus grant signals used by DMA controllers.

Install the board carefully using anti-static protection. Do not force the board. If it does not seat properly, remove the board and determine the cause. Observe the P1 connector if possible to see that it is seating properly.

Now reapply power with the DVME-601 installed. Confirm that your operating system boots up normally. Verify the memory size message if it is normally present. The DVME-601 front panel green LED lamp should light to confirm power-up self testing of its CPU, memory and peripheral controller. If your operating system fails to boot up normally, turn power off immediately and review the board configuration information in this manual.

Do not make any connections to the front panel until you have read this manual. Avoid any live analog connections with power off.

# I/O CONNECTIONS AND THE MONITOR

## 3.0 Introduction

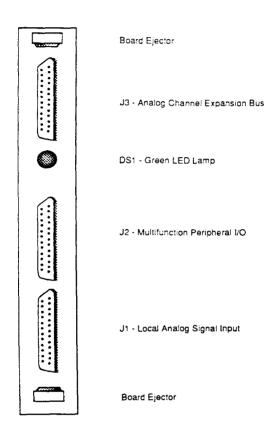

The DVME-601 includes three front panel connectors and a P1 VMEbus connector. The front panel connectors are female 25-pin type DB-25S. They include 4-40 threaded strain reliefs for optional hooded mating DB-25P connectors. The rear VMEbus connector is a male 96-pin 3-row DIN type. A programmable Light Emitting Diode (LED) green lamp is also mounted on the front panel. The layout for the front panel is shown in Figure 3.0.

Figure 3.0 Front Panel Connector Locations

## 3.1 Local Analog Signal Inputs

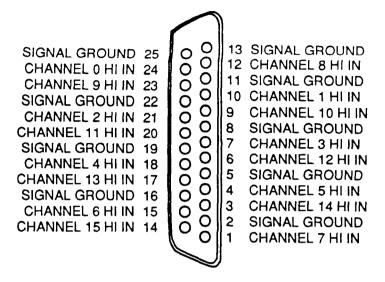

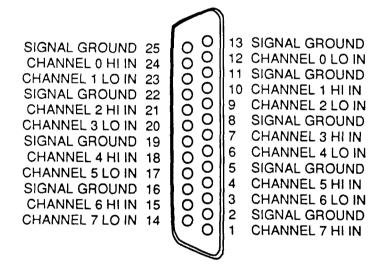

The J1 connector accepts voltage signals for on-board analog input channels. The connector pinout is arranged to accept either single-ended or differential inputs depending on the board jumpers. For single-ended inputs (Figure 3.1), channel numbering is 0 through 15. Differential inputs (Figure 3.2) are channels 0 through 7. Both figures show the pin numbering as viewed looking toward the front panel.

Figure 3.1 Local Single-ended Analog Inputs - Connector J1

The grounds are arranged so that a ground is shared by every two channels.

Figure 3.2 Local Differential Analog Inputs - Connector J1

Pin numbering is arranged as viewed looking toward the front panel.

## 3.1.1 Typical Analog Input Wiring

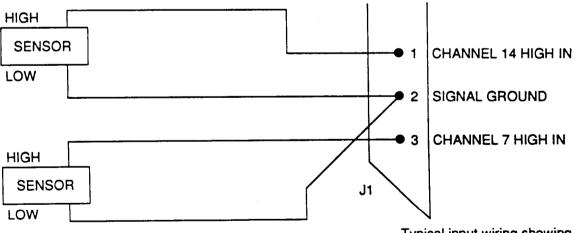

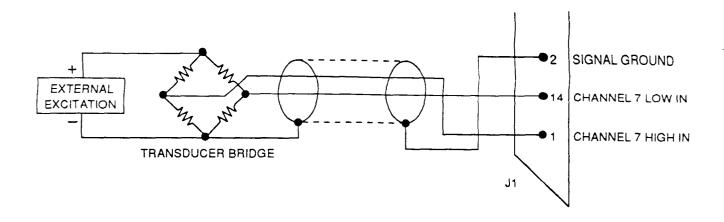

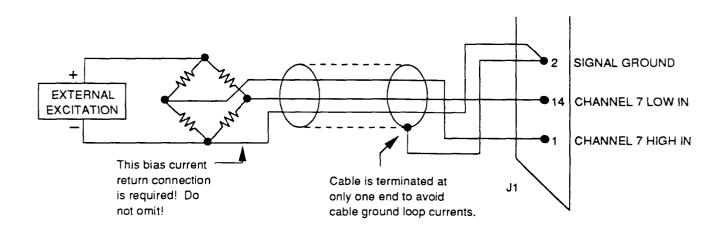

Figures 3.3 and 3.4 show typical input wiring used with both single-ended and differential input sources. Note that single-ended inputs share one ground for approximately every two input channels. The following guidelines should be observed:

1. All inputs are non-isolated. All inputs must remain within the common mode voltage range at all times during measurement. This is accomplished in your application by providing a bias current return path to ground through the sensor or bridge.

If you need fully isolated, floating inputs to the DVME-601, consider connecting it to the DVME-643 slave multiplexer board.

- 2. For the single-ended inputs, two external connections (Hi and signal ground) are required per channel. On differential inputs, three connections are required per channel (Hi, Lo, Ground). Do not omit the ground connection or low input on differential inputs.

- 3. Use a single point system analog ground connection. Multiple ground paths form ground loops which collect noise which is proportional to the loop area and noise field strength.

- 4. If you use shielded cable, avoid carrying any current on the shield. This will prevent noise induced on the signal leads. One way to do this is to terminate the shield only at the grounded end. If so, you will still need a bias return path for the bridge ground. See Figure 3.5.

- 5. Avoid high amplitude wideband noise on input signals. The narrow aperture and fast acquisition time of the DVME-601 sample/hold amplifier and A/D converter will faithfully digitize the noise as well as the signal. Large amplitude noise may also be partially rectified in input circuits, producing dc offset errors. Consider external filtering for high noise inputs.

- 6. Fully attenuate all input signal frequency spectra which are at or above one half the sample rate of the converter. This will avoid alias noise. Use multipole filters if necessary.

Typical input wiring showing two sensors sharing a ground. Terminate both ground leads at the connector.

Figure 3.3 Single-ended Input Wiring

Figure 3.4 Differential Input Wiring

Figure 3.5 Differential Bridge Wiring

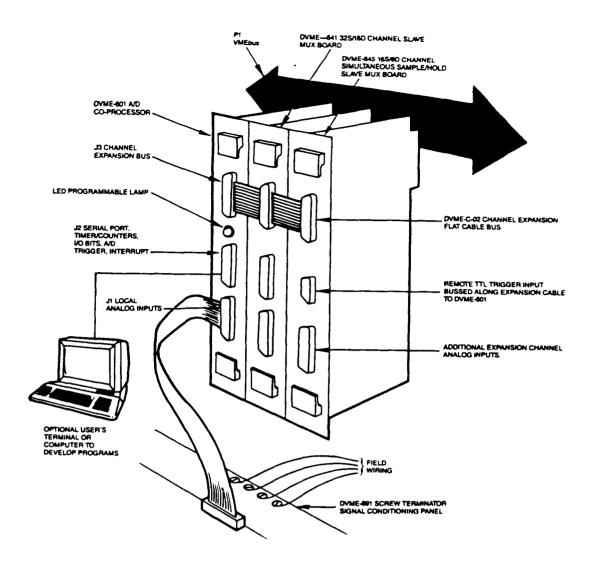

#### 3.2 A/D Channel Expansion Bus

The DVME-601 offers channel expansion for additional inputs beyond the local on-board channels. The maximun limit is 10 slave MUX boards. The DVME-601 local channels must be configured for differential inputs before using channel expansion. A flat cable channel expansion bus is provided on the DVME-601's J3 front panel connector. It plugs into DATEL's optional slave multiplexer boards installed in slots adjacent to the DVME-601 or in a nearby VME chassis. The pinout of the J3 connector is shown in Figure 3.6. An overall view of front panel connections including the channel expansion bus is shown in Figure 3.7.

#### NOTICE

Channel expansion is normally disconnected:

Starting with PC board artwork Revision F, the expansion analog inputs are supplied disconnected. Connect solder gaps SG1 and SG2 on the non-component side of the board to enable expansion inputs. Use a low wattage soldering iron to avoid damaging the board. This operation should only be done by an experienced person. If you anticipate any difficulty in doing this, contact DATEL before shipment.

Pin numbering is arranged as viewed looking toward the front panel.

Figure 3.6 Analog Channel Expansion Bus - Connector J3

#### 3.2.1 Channel Expansion Multiplexer Boards

The slave MUX boards include the DVME-641 32S/16D channel high speed MUX, the DVME-643 8D channel low level isolated MUX (for sensors such as thermocouples, RTD's, 4-20 mA loops, etc.) and the DVME-645 16S/8D channel simultaneous sample/hold MUX. The DVME-645 is especially suited to array processing and DSP applications.

The MUX boards use +5V dc power from the VMEbus to run on-board dc/dc power converters. This generates power for linear circuits. Otherwise the MUX boards do not connect to the VMEbus.

Channel address programming is discussed in Section 4. The channel expansion bus allows the DVME-601 to directly control each slave MUX board and carries three classes of signals. They are:

- 1. The bus includes 8-bit channel address outputs from the DVME- 601's current channel address register. The eight address outputs are J3 pins 10 through 13 and 22 through 25.

- 2. Buffered high level switched differential analog input signals are supplied on pins J3-1 and J3-14. These inputs use J3-2 and J3-15 as grounds. A local multiplexer on the DVME-601 switches these inputs into the Instrumentation Amplifier for A/D conversion.

- 3. Also included are control and handshake lines, an external A/D start trigger input and grounds.

Channel addresses are distributed to all MUX boards along the bus. The 8-bit binary address code controls up to 256 total single-ended or differential channels. The channel addresses are numbered 0 through 255 and the first 8 differential or 16 single-ended channels are always located on the DVME-601.

Individual multiplexer boards include base address decoder switches which must be set properly before installation. Address selection logic allows each MUX board to respond to a unique range of addresses. When selected, a MUX board connects its analog outputs to the differential input in pins J3-1 and 14. These inputs are digitized by the DVME-601's A/D converter. All other de-selected MUX boards disconnect their analog outputs from the bus until they are addressed. This analog multiplexing occurs at very high speed. There is no speed penalty addressing a range of contiguous channels over several MUX boards. Nor do contiguously addressed MUX boards have to be adjacent to each other or even in the same VME rack housing.

Both single-ended and differential inputs may be mixed on different MUX boards for the same bus while local DVME-601 channels must remain differential. For diagnostics, a LED lamp on each MUX board lights when that board is addressed.

DATEL offers 2- and 3-connector cables, models DVME-C-01 and -02, to connect one or two slave MUX boards and users may fabricate flat cables for up to 10 boards total.

Pin J3-17 on the expansion bus is a TTL, open-collector, negative-true A/D trigger input. The A/D start input to the DVME-601 may be initiated from the trigger input on any multiplexer board. A pullup resistor to +5V is supplied on the DVME-601. A single TTL hardware trigger from an external event will start either one A/D sample and host interrupt or a scan of channels on one or more boards. The trigger must be 100 nanoseconds minimum to 2 microseconds maximum. Triggering occurs on the falling edge.

Important: Disconnect the expansion trigger input on J3-17 if the local Pacer trigger connection (J2-19 to J2-10) is used.

Scan addressing is fully controlled from the DVME-601's start and final channel address registers. Scan address boundaries are independent of MUX board address boundaries. Thus one MUX board trigger input may start conversion for channels on other MUX boards.

Alternatively, automatic channel sequencing and A/D conversion may be started from a DVME-601 Pacer timer in the 68901 controller. The timer output must be jumpered to the trigger input on the J3 connector. Or a software command from the host will start the A/D.

An open collector wire-OR'd settling delay control line input is provided on pin J3-20. A settling delay one-shot output from each MUX board will delay the actual A/D conversion to synchronize settling times of low level preamplifiers on the DVME-643 slave MUX boards. High level DVME-641 and -645 MUX boards do not use this settling delay. If noise on this settling input causes random A/D delays, this line may be diconnected at the A/D board. Through appropriate host A/D software, board addressing and input range selection, it is even possible to mix high and low level MUX input boards on the same bus.

Figure 3.7 Front Panel Cabling and Channel Expansion

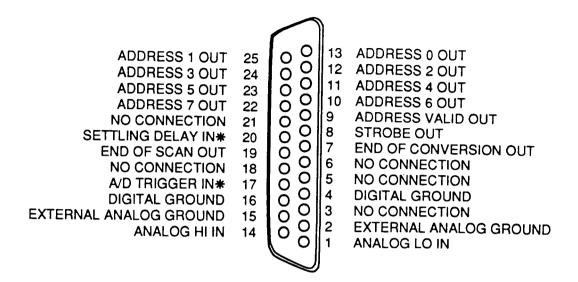

#### 3.3 VMEbus Connections

The interface to the VME host is made through the P1 connector, shown in Figure 3.8. This interface uses the IEEE-P1014/D1.0 specification. Note that the Interrupt Acknowledge connections are fully implemented and that internal DVME-601 logic uses the 16 MHz SYSCLK. The  $\pm 12$  Volt power pins are used if the serial port Monitor terminal is connected.

|        | Row A    | Row B          | Row C     |

|--------|----------|----------------|-----------|

| Pin    | Signal   | Signal         | Signal    |

| Number | Mnemonic | Mnemonic       | Mnemonic  |

| 1      | D00      | BBSY*          | D08       |

| 2      | D01      | BCLR*          | D09       |

| 3      | D02      | ACFAIL*        | D10       |

| 4      | D03      | BG0IN*         | D11       |

| 5      | D04      | BG0OUT*        | D12       |

| 6      | D05      | BG1IN*         | D13       |

| 7      | D06      | BG1OUT*        | D14       |

| 8      | D07      | BG2IN <b>∗</b> | D15       |

| 9      | GND      | BG2OUT*        | GND       |

| 10     | SYSCLK   | BG3IN*         | SYSFAIL*  |

| 11     | GND      | BG3OUT*        | BEAR*     |

| 12     | DS1*     | BR0*           | SYSRESET* |

| 13     | DS0*     | BR1 <b>∗</b>   | LWORD*    |

| 14     | WRITE*   | BR2 <b>∗</b>   | AM5       |

| 15     | GND      | BR3*           | A23       |

| 16     | DTACK*   | AM0            | A22       |

| 17     | GND      | AM1            | A21       |

| 18     | AS*      | AM2            | A20       |

| 19     | GND      | AM3            | A19       |

| 20     | IACK*    | GND            | A18       |

| 21     | IACKIN*  | SERCLK         | A17       |

| 22     | IACKOUT* | SERDAT         | A16       |

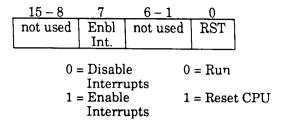

| 23     | AM4      | GND            | A15       |